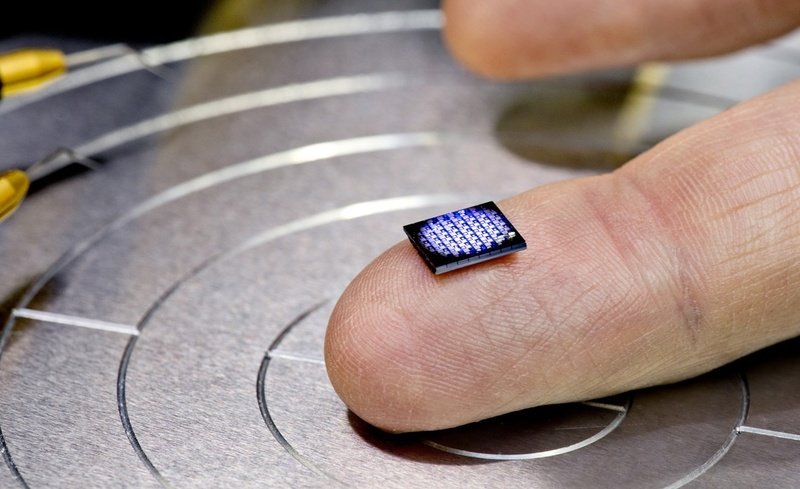

IBM представила самый компактный чип

IBM сконструировала первый тестовый чип с 2-нанометровым техпроцессом с самой компактной на сегодняшний день упаковкой транзисторов. Микросхема поступит в серийное производство не раньше 2024 года.

Новая микросхема построена на архитектуре GAA (Gate-all-around): затвор транзистора со всех сторон окружает канал, состоящий из трех пластин высотой 5 нанометров и длиной 12 нанометров. На квадратный миллиметр чипа приходится 333 миллиона транзисторов. Пресс-служба IBM утверждает, что новая микросхема имеет почти на 50 % большую производительность и на 75 % меньшее энергопотребление, чем самый эффективный до этого 7-нанометровый техпроцесс. Однако компания не указывает, с продуктом какого производителя она сравнивает свою разработку.

Уменьшение размеров транзисторов и его элементов улучшает характеристики работающих на них устройств: энергоэффективность и скорость работы. Например, на чипе можно поместить большее количество транзисторов, расстояние между ними станет меньше, и сигнал по микросхеме будет проходить быстрее.

Раньше техпроцессом обозначали длину затвора транзистора — он регулирует поток электронов. В какой-то момент стало ясно, что дальше уменьшать затворы невозможно — электроны будут проскакивать через них. Тогда производители увеличили длину и площадь канала, что позволило проходить по нему большему количеству частиц. При этом сравнение чипов по техпроцессу стало маркетинговым ходом, не имеющим физического смысла. Сейчас важная и релевантная характеристика полупроводниковой электроники — плотность транзисторов на микросхеме. По данным AnandTech, у нового чипа она на 14 % выше, чем у 3-нанометрового от компании TSMC.